16-tavolaj PCB provizas la kompleksecon kaj flekseblecon postulataj de modernaj elektronikaj aparatoj. Kvalifikita dezajno kaj elekto de stakantaj sekvencoj kaj intertavolaj konektmetodoj estas kritikaj por atingi optimuman tabuladon. En ĉi tiu artikolo, ni esploros konsiderojn, gvidliniojn kaj plej bonajn praktikojn por helpi dizajnistojn kaj inĝenierojn krei efikajn kaj fidindajn 16-tavolajn cirkvitojn.

1.Komprenante la Bazojn de 16-tavola PCB-Stakado-Sekvenco

1.1 Difino kaj celo de stakiga ordo

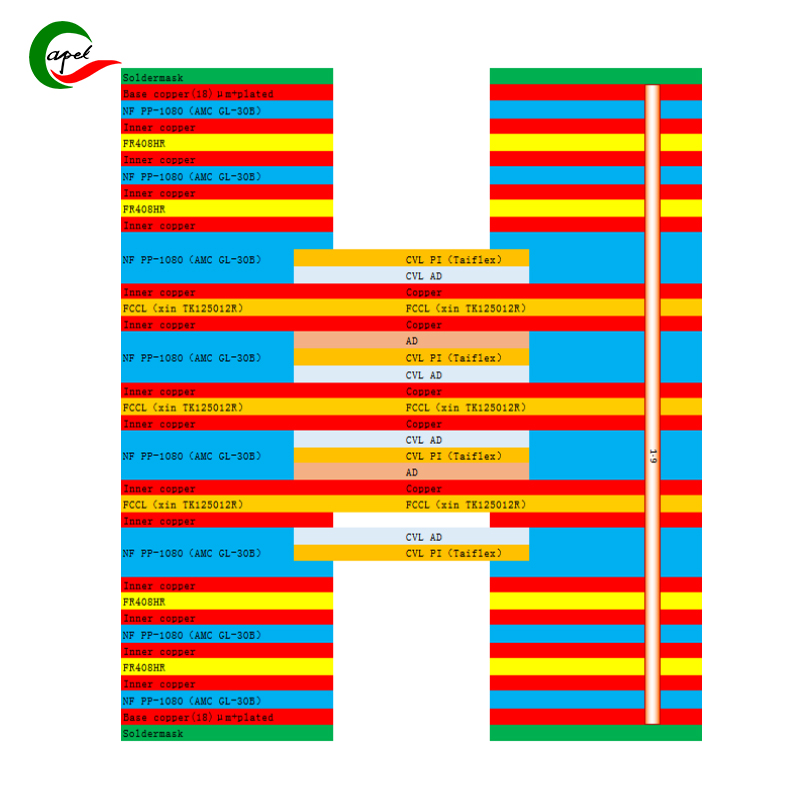

Stakiga sekvenco rilatas al la aranĝo kaj ordo en kiuj materialoj kiel kupro kaj izolaj tavoloj estas lamenigitaj kune por formi plurtavolan cirkviton. la stako.

La ĉefa celo de la stakiga sekvenco estas atingi la postulatajn elektrajn kaj mekanikajn ecojn de la tabulo. Ĝi ludas esencan rolon en determini la impedancon de cirkvittabulo, signalintegrecon, potencodistribuon, termikan administradon kaj produktadeblecon. La stakiga sekvenco ankaŭ influas la ĝeneralan rendimenton, fidindecon kaj fabrikeblecon de la tabulo.

1.2 Faktoroj influantaj la stakigan sekvencon desegno: Estas pluraj faktoroj por konsideri dum dizajnas la stakigan sekvencon de

16-tavola PCB:

a) Elektraj konsideroj:La aranĝo de signalo, potenco kaj grundaj aviadiloj devus esti optimumigita por certigi taŭgan signalintegrecon, impedanckontrolon kaj redukton de elektromagneta interfero.

b) Termikaj konsideroj:La lokigo de potencaj kaj grundaj aviadiloj kaj la inkludo de termikaj vojoj helpas efike disipi varmon kaj konservi la optimuman funkcian temperaturon de la komponento.

c) Limoj de fabrikado:La stakiga sekvenco elektita devus konsideri la kapablojn kaj limigojn de la PCB-produktadprocezo, kiel ekzemple materiala havebleco, nombro da tavoloj, borila bildformato,kaj vicigi precizecon.

d) Kosto-Optimumigo:La elekto de materialoj, nombro da tavoloj kaj stak-supren komplekseco devus esti kongrua kun la projekta buĝeto certigante la postulatan agadon kaj fidindecon.

1.3 Oftaj specoj de 16-tavolaj cirkvittablaj staksekvencoj: Estas pluraj oftaj staksekvencoj por 16-tavolaj

PCB, depende de la dezirata agado kaj postuloj. Iuj oftaj ekzemploj inkluzivas:

a) Simetria stakiga sekvenco:Tiu sekvenco implikas meti signaltavolojn simetrie inter potenco kaj grundtavoloj por atingi bonan signalintegrecon, minimuman krucparoladon, kaj ekvilibran varmodissipadon.

b) Sinsekva stakiga sekvenco:En tiu sekvenco, la signaltavoloj estas sinsekve inter la potenco kaj grundaj tavoloj. Ĝi disponigas pli grandan kontrolon de tavola aranĝo kaj estas utila por renkonti specifajn signalajn integrecpostulojn.

c) Miksita stakiga ordo:Ĉi tio implikas kombinaĵon de simetriaj kaj sinsekvaj stakigaj ordoj. Ĝi permesas personigon kaj optimumigon de la aranĝo por specifaj partoj de la tabulo.

d) Signal-sentema stakiga sekvenco:Tiu sekvenco metas sentemajn signaltavolojn pli proksime al la grunda ebeno por pli bona brua imuneco kaj izoliteco.

2. Ŝlosilaj Konsideroj por 16-tavola PCB Stacking Sekvenselektado:

2.1 Konsideroj pri signala integreco kaj potenco integreco:

La stakiga sekvenco havas signifan efikon al la signala integreco kaj potenco integreco de la tabulo. Konvena lokigo de signalo kaj potenco/teraj aviadiloj estas kritika por minimumigi la riskon de signalmisprezento, bruo kaj elektromagneta interfero. Ĉefaj konsideroj inkluzivas:

a) Lokigo de signala tavolo:Altrapidaj signaltavoloj devas esti metitaj proksime al la grunda aviadilo por disponigi malalt-induktan revenan vojon kaj minimumigi bruan kupladon. Signaltavoloj ankaŭ devas esti zorge aranĝitaj por minimumigi signalan dekliniĝon kaj longokongruon.

b) Distribuo de elektraj aviadiloj:La stakiga sekvenco devus certigi adekvatan elektran ebenan distribuon por subteni povintegrecon. Sufiĉaj potenco kaj grundaviadiloj devus esti strategie metitaj por minimumigi tensiofalojn, impedancmalkontinuecojn, kaj bruokupladon.

c) Malkunligaj Kondensiloj:Taŭga lokigo de malkunligaj kondensiloj estas kritika por certigi taŭgan transdonon de potenco kaj minimumigi elektroprovizobruon. La stakiga sekvenco devus disponigi proksimecon kaj proksimecon de la malkunligaj kondensiloj al la potenco kaj grundaj aviadiloj.

2.2 Termika administrado kaj varmodissipado:

Efika termika administrado estas kritika por certigi fidindecon kaj efikecon de cirkvitotabulo. La stakiga sekvenco devus enkalkuli la bonordan allokigon de potenco kaj grundaviadiloj, termikaj vojoj, kaj aliaj malvarmigaj mekanismoj. Gravaj konsideroj inkluzivas:

a) Distribuo de elektraj aviadiloj:Adekvata distribuado de potenco kaj grundaj aviadiloj tra la stako helpas direkti varmon for de sentemaj komponantoj kaj certigas unuforman temperaturdistribuon tra la tabulo.

b) Termikaj vojoj:La stakiga sekvenco devus enkalkuli efikan termikon per allokigo faciligi varmodisipadon de la interna tavolo ĝis la ekstera tavolo aŭ varmolavujo. Ĉi tio helpas malhelpi lokalizitajn varmajn punktojn kaj certigas efikan varmodissipadon.

c) Lokigo de komponantoj:Stakiga sekvenco devus konsideri la aranĝon kaj proksimecon de hejtaj komponantoj por eviti recalentiĝon. Ĝusta paraleligo de komponantoj kun malvarmigaj mekanismoj kiel varmegaj lavujoj aŭ ventoliloj ankaŭ devus esti pripensita.

2.3 Produktadlimoj kaj kostooptimumigo:

La stakiga sekvenco devas konsideri produktadlimojn kaj kostooptimumigon, ĉar ili ludas gravan rolon en la farebleco kaj pagebleco de la tabulo. Konsideroj inkluzivas:

a) Materiala havebleco:La stakiga sekvenco elektita devus esti kongrua kun la havebleco de materialoj kaj ilia kongruo kun la elektita PCB-produktadprocezo.

b) Nombro de tavoloj kaj komplekseco:La staksekvenco devus esti desegnita ene de la limoj de la elektita PCB-produktadprocezo, konsiderante faktorojn kiel ekzemple nombro da tavoloj, borila bildformato, kaj vicigprecizeco.

c) Kostooptimumigo:La staksekvenco devus optimumigi la uzon de materialoj kaj redukti produktadkompleksecon sen endanĝerigi la postulatan rendimenton kaj fidindecon. Ĝi devus celi minimumigi kostojn asociitajn kun materiala malŝparo, proceza komplekseco kaj kunigo.

2.4 Tavola paraleligo kaj signala krucparolado:

La stakiga sekvenco devus trakti tavolajn paraleliĝproblemojn kaj minimumigi signalinterkruciĝon kiu povas negative influi signalintegrecon. Gravaj konsideroj inkluzivas:

a) Simetria stakiĝo:Simetria stakiĝo de signalaj tavoloj inter potencaj kaj grundaj tavoloj helpas minimumigi kunigon kaj redukti interkruciĝon.

b) Diferenciala parvojigo:La stapliga sekvenco devus permesi al la signaltavoloj esti konvene vicigitaj por efika vojigo de altrapidaj diferencigaj signaloj. Ĉi tio helpas konservi signalan integrecon kaj minimumigi interkruciĝon.

c) Signapartigo:La stakiga sekvenco devus pripensi la apartigon de sentemaj analogaj kaj ciferecaj signaloj por redukti krucparoladon kaj interferon.

2.5 Impedancia kontrolo kaj RF/mikroonda integriĝo:

Por RF/mikroondaj aplikoj, la staksekvenco estas kritika por atingi taŭgan impedanckontrolon kaj integriĝon. Ĉefaj konsideroj inkluzivas:

a) Kontrolita impedanco:La stakiga sekvenco devus enkalkuli kontrolitan impedancdezajnon, enkalkulante faktorojn kiel ekzemple spurlarĝo, dielektrika dikeco, kaj tavolaranĝo. Ĉi tio certigas ĝustan signalan disvastigon kaj impedancan kongruon por RF/mikroondaj signaloj.

b) Lokigo de signala tavolo:RF/mikroondaj signaloj devus esti strategie metitaj proksime al la ekstera tavolo por minimumigi interferon de aliaj signaloj kaj disponigi pli bonan signaldisvastiĝon.

c) RF Ŝirmado:La stakiga sekvenco devus inkluzivi taŭgan allokigon de grundaj kaj ŝirmaj tavoloj por izoli kaj protekti RF/mikroondajn signalojn de interfero.

3.Intertavolaj Konekto-Metodoj

3.1 Tra truoj, blindaj truoj kaj entombigitaj truoj:

Vias estas vaste uzataj en dezajno de presitaj cirkvitoj (PCB) kiel rimedo por konekti malsamajn tavolojn. Ili estas boritaj truoj tra ĉiuj tavoloj de la PCB kaj estas tegitaj por disponigi elektran kontinuecon. Tra truoj disponigas fortan elektran konekton kaj estas relative facilaj por fari kaj ripari. Tamen, ili postulas pli grandajn borilpecojn, kiuj okupas valoran spacon sur la PCB kaj limigas vojajn elektojn.

Blindaj kaj entombigitaj vojoj estas alternativaj intertavolaj konektmetodoj kiuj ofertas avantaĝojn en spaca utiligo kaj vojigfleksebleco.

Blindaj vojoj estas boritaj de la PCB-surfaco kaj finiĝas en internaj tavoloj sen trapasi ĉiujn tavolojn. Ili permesas ligojn inter apudaj tavoloj lasante pli profundajn tavolojn netuŝitaj. Ĉi tio permesas pli efikan uzon de tabulospaco kaj reduktas la nombron da bortruoj. Entombigitaj vojoj, aliflanke, estas truoj kiuj estas tute enfermitaj ene de la internaj tavoloj de la PCB kaj ne etendiĝas al la eksteraj tavoloj. Ili disponigas ligojn inter internaj tavoloj sen influi la eksterajn tavolojn. Entombigitaj travojoj havas pli grandajn spacŝparajn avantaĝojn ol tra-truoj kaj blindaj travojoj ĉar ili ne okupas ajnan spacon en la ekstera tavolo.

La elekto de tratruoj, blindaj vojoj kaj entombigitaj vojoj dependas de la specifaj postuloj de la PCB-dezajno. Tra truoj estas tipe uzitaj en pli simplaj dezajnoj aŭ kie fortikeco kaj ripareblo estas primaraj konzernoj. En alt-densecaj dezajnoj kie spaco estas kritika faktoro, kiel ekzemple porteblaj aparatoj, inteligentaj telefonoj kaj tekkomputiloj, blindaj kaj entombigitaj vojoj estas preferitaj.

3.2 Mikroporo kajHDI-teknologio:

Mikrovias estas malgrandaj diametraj truoj (kutime malpli ol 150 mikronoj) kiuj disponigas alt-densecajn intertavolligojn en PCBoj. Ili ofertas signifajn avantaĝojn en miniaturigo, signalintegreco kaj vojigfleksebleco.

Mikrovioj povas esti dividitaj en du tipojn: tra-truaj mikrovioj kaj blindaj mikrovojoj. Microvias estas konstruitaj per borado de truoj de la supra surfaco de la PCB kaj etendiĝanta tra ĉiuj tavoloj. Blindaj mikrovojoj, kiel la nomo sugestas, nur etendiĝas al specifaj internaj tavoloj kaj ne penetras ĉiujn tavolojn.

Alt-denseca interkonekto (HDI) estas teknologio, kiu uzas mikrovojojn kaj altnivelajn fabrikajn teknikojn por atingi pli altan cirkvitan densecon kaj rendimenton. HDI-teknologio permesas la allokigon de pli malgrandaj komponentoj kaj pli malloza vojigo, rezultigante pli malgrandajn formfaktorojn kaj pli altan signalintegrecon. HDI-teknologio ofertas plurajn avantaĝojn super tradicia PCB-teknologio laŭ miniaturigo, plibonigita signaldisvastigo, reduktita signalmisprezento, kaj plifortigita funkcieco. Ĝi permesas plurtavolajn dezajnojn kun multoblaj mikrovojoj, tiel mallongigante interkonektajn longojn kaj reduktante parazitajn kapacitancon kaj induktancon.

HDI-teknologio ankaŭ ebligas la uzon de progresintaj materialoj kiel altfrekvencaj lamenaĵoj kaj maldikaj dielektraj tavoloj, kiuj estas kritikaj por RF/mikroondaj aplikoj. Ĝi provizas pli bonan impedanckontrolon, reduktas signalan perdon kaj certigas fidindan altrapidan signalan transdonon.

3.3 Intertavolaj konektmaterialoj kaj procezoj:

La elekto de intertavolaj konektmaterialoj kaj teknikoj estas kritika por certigi bonan elektran rendimenton, mekanikan fidindecon kaj fabrikeblecon de PCB-oj. Kelkaj ofte uzitaj intertavolaj ligmaterialoj kaj teknikoj estas:

a) Kupro:Kupro estas vaste uzata en konduktaj tavoloj kaj vojoj de PCB-oj pro sia bonega kondukteco kaj lutebleco. Ĝi estas kutime tegita sur la truo por disponigi fidindan elektran konekton.

b) Lutado:Lutadoteknikoj, kiel ekzemple ondolutado aŭ reflua lutado, ofte kutimas fari elektrajn ligojn inter tra truoj sur PCBoj kaj aliaj komponentoj. Apliku lutpaston al la vojo kaj apliku varmegon por fandi la lutaĵon kaj formi fidindan ligon.

c) Electroplating:Electroplating-teknikoj kiel ekzemple senelektrola kuproteksado aŭ elektroliza kupro estas uzataj por platigi vojojn por plifortigi konduktivecon kaj certigi bonajn elektrajn ligojn.

d) Ligo:Ligado-teknikoj, kiel ekzemple glua ligado aŭ termokunprema ligado, kutimas kunligi tavoligitajn strukturojn kune kaj krei fidindajn interligojn.

e) Dielektrika materialo:La elekto de dielektrika materialo por la PCB-stakado estas kritika por intertavolaj ligoj. Altfrekvencaj lamenaĵoj kiel ekzemple FR-4 aŭ Rogers lamenaĵoj ofte estas uzitaj por certigi bonan signalintegrecon kaj minimumigi signalperdon.

3.4 Transsekca dezajno kaj signifo:

La trans-sekca dezajno de la PCB-stako determinas la elektrajn kaj mekanikajn trajtojn de la ligoj inter tavoloj. Ĉefaj konsideroj por sekca dezajno inkludas:

a) Tavola aranĝo:La aranĝo de signalo, potenco, kaj grundaj aviadiloj ene de PCB-stako influas signalintegrecon, potencointegrecon kaj elektromagnetan interferon (EMI). Ĝusta lokigo kaj vicigo de signaltavoloj kun potencaj kaj grundaj aviadiloj helpas minimumigi bruan kupladon kaj certigi malaltajn induktan revenvojojn.

b) Impedancia kontrolo:Sekca dezajno devus enkalkuli kontrolitajn impedancpostulojn, precipe por altrapidaj ciferecaj aŭ RF/mikroondaj signaloj. Tio implikas konvenan elekton de dielektraj materialoj kaj dikecoj por atingi la deziratan karakterizan impedancon.

c) Termika administrado:La sekca dezajno devus konsideri efikan varmodissipadon kaj termikan administradon. Konvena allokigo de potenco kaj grundaj aviadiloj, termikaj vojoj, kaj komponentoj kun malvarmigaj mekanismoj (kiel ekzemple varmolavujoj) helpas disipi varmecon kaj konservi optimumajn funkciigadtemperaturojn.

d) Mekanika fidindeco:Sekcia dezajno devus konsideri mekanikan fidindecon, precipe en aplikoj kiuj povas esti submetitaj al termika biciklado aŭ mekanika streso. Ĝusta elekto de materialoj, kunligaj teknikoj kaj stak-agordo helpas certigi la strukturan integrecon kaj fortikecon de la PCB.

4.Dezajna Gvidlinioj por 16-Tavola PCB

4.1 Tavola asigno kaj distribuo:

Dum desegnado de 16-tavola cirkvito, gravas zorge asigni kaj distribui la tavolojn por optimumigi rendimenton kaj signalan integrecon. Jen kelkaj gvidlinioj por nivela atribuo

kaj distribuo:

Determini la nombron da signaltavoloj bezonataj:

Konsideru la kompleksecon de la cirkvitodezajno kaj la nombron da signaloj, kiuj devas esti direktitaj. Asignu sufiĉe da signaltavoloj por alĝustigi ĉiujn postulatajn signalojn, certigante taŭgan vojigspacon kaj evitante troankongesto. Asignu terajn kaj potencajn aviadilojn:

Asignu almenaŭ du internajn tavolojn al grundaj kaj potencaj aviadiloj. Tera ebeno helpas disponigi stabilan referencon por signaloj kaj minimumigas elektromagnetan interferon (EMI). La elektra aviadilo disponigas malalt-impedancan elektran distribuan reton kiu helpas minimumigi tensiofalojn.

Apartaj sentemaj signaltavoloj:

Depende de la apliko, povas esti necese apartigi sentemajn aŭ altrapidajn signaltavolojn de bruaj aŭ alt-potencaj tavoloj por malhelpi interferon kaj interkruciĝon. Ĉi tio povas esti farita metante diligentajn grundojn aŭ potencajn aviadilojn inter ili aŭ uzante izolaj tavoloj.

Egale distribuu signalajn tavolojn:

Distribuu signalajn tavolojn egale tra la tabulo por minimumigi kunigon inter apudaj signaloj kaj konservi signalintegrecon. Evitu meti signalajn tavolojn unu apud la alia en la sama stak-areo por minimumigi intertavolan interkruciĝon.

Konsideru altfrekvencajn signalojn:

Se via dezajno enhavas altfrekvencajn signalojn, konsideru meti la altfrekvencajn signaltavolojn pli proksime al la eksteraj tavoloj por minimumigi transmisiajn efikojn kaj redukti disvastigajn prokrastojn.

4.2 Vokado kaj signalvojigo:

Vojigo kaj signalspurdezajno estas kritikaj por certigi taŭgan signalintegrecon kaj minimumigi interferon. Jen kelkaj gvidlinioj por aranĝo kaj signalvojigo sur 16-tavolaj cirkvitoj:

Uzu pli larĝajn spurojn por alt-kurantaj signaloj:

Por signaloj kiuj portas altan kurenton, kiel potenco kaj grundaj konektoj, uzu pli larĝajn spurojn por minimumigi reziston kaj tensiofalon.

Kongrua impedanco por altrapidaj signaloj:

Por altrapidaj signaloj, certigu, ke la spura impedanco kongruas kun la karakteriza impedanco de la transdona linio por malhelpi reflektojn kaj signalan malfortiĝon. Uzu kontrolitajn impedancajn dezajnteknikojn kaj korektu spurlarĝkalkulojn.

Minimumu spurlongojn kaj interkruciĝajn punktojn:

Konservu spurlongojn kiel eble plej mallongajn kaj reduktu la nombron da interkruciĝpunktoj por redukti parazitajn kapacitancon, induktancon kaj interferon. Optimumigu komponan lokigon kaj uzu dediĉitajn vojajn tavolojn por eviti longajn kaj kompleksajn spurojn.

Apartaj altrapidaj kaj malaltrapidaj signaloj:

Apartigu altrapidajn kaj malaltrapidajn signalojn por minimumigi la efikon de bruo sur altrapidaj signaloj. Metu altrapidajn signalojn sur diligentajn signaltavolojn kaj tenu ilin for de alta potenco aŭ bruaj komponantoj.

Uzu diferencigajn parojn por altrapidaj signaloj:

Por minimumigi bruon kaj konservi signalintegrecon por altrapidaj diferencigaj signaloj, uzu diferencigajn parvojajn teknikojn. Konservu la impedancon kaj longon de diferencigaj paroj kongruaj por malhelpi signalo-dekliniĝon kaj interkruciĝon.

4.3 Grunda tavolo kaj potenca tavolo distribuo:

Ĝusta distribuado de grundaj kaj potencaj aviadiloj estas kritika por atingi bonan potencan integrecon kaj redukti elektromagnetan interferon. Jen kelkaj gvidlinioj por grundaj kaj elektraj aviadilaj taskoj sur 16-tavolaj cirkvitoj:

Asignu diligentajn grundajn kaj potencajn aviadilojn:

Asignu almenaŭ du internajn tavolojn por dediĉitaj grundaj kaj potencaj aviadiloj. Ĉi tio helpas minimumigi grundajn buklojn, redukti EMI kaj disponigi malalt-impedancan revenvojon por altfrekvencaj signaloj.

Apartaj ciferecaj kaj analogaj teraviadiloj:

Se la dezajno havas ciferecajn kaj analogajn sekciojn, oni rekomendas havi apartajn grundajn aviadilojn por ĉiu sekcio. Ĉi tio helpas minimumigi bruokupladon inter la ciferecaj kaj analogaj sekcioj kaj plibonigas signalintegrecon.

Metu grundajn kaj potencajn aviadilojn proksime al signalaviadiloj:

Metu grundajn kaj potencajn aviadilojn proksime al la signalaviadiloj, kiujn ili nutras por minimumigi buklareon kaj redukti bruon.

Uzu plurajn vojojn por elektraj aviadiloj:

Uzu multoblajn vojojn por konekti potencajn aviadilojn por egale distribui potencon kaj redukti potencon de impedanco. Ĉi tio helpas minimumigi provizajn tensiofalojn kaj plibonigas potencon integrecon.

Evitu mallarĝajn kolojn en elektraj aviadiloj:

Evitu mallarĝajn kolojn en elektraj aviadiloj, ĉar ili povas kaŭzi nunan amasiĝon kaj pliigi reziston, rezultigante tensiofalojn kaj neefikecojn de elektraj aviadiloj. Uzu fortajn ligojn inter malsamaj areoj de elektraj aviadiloj.

4.4 Termika kuseneto kaj per lokigo:

Ĝusta lokigo de termikaj kusenetoj kaj vojoj estas kritika por efike disipi varmecon kaj malhelpi komponentojn de trovarmiĝo. Jen kelkaj gvidlinioj por termika kuseneto kaj per lokigo sur 16-tavolaj cirkvitoj:

Metu termikan kuseneton sub varmegajn komponantojn:

Identigu la varmegan komponanton (kiel potencan amplifilon aŭ alt-potencan IC) kaj metu la termikan kuseneton rekte sub ĝi. Ĉi tiuj termikaj kusenetoj disponigas rektan termikan vojon por transdoni varmecon al la interna termika tavolo.

Uzu plurajn termikajn vojojn por varmo disipado:

Uzu multoblajn termikajn vojojn por konekti la termikan tavolon kaj eksteran tavolon por disponigi efikan varmodissipadon. Ĉi tiuj vojoj povas esti metitaj en ŝanceligita ŝablono ĉirkaŭ la termika kuseneto por atingi eĉ varmodistribuon.

Konsideru termikan impedancon kaj tavolan amasigon:

Kiam vi desegnas termikajn vojojn, konsideru la termikan impedancon de la tabulo-materialo kaj tavola stackup.Optimigu per grandeco kaj interspaco por minimumigi termikan reziston kaj maksimumigi varmegan disipadon.

4.5 Komponanta Lokigo kaj Signala Integreco:

Taŭga komponentlokigo estas kritika por konservi signalintegrecon kaj minimumigi interferon. Jen kelkaj gvidlinioj por meti komponantojn sur 16-tavolan cirkviton:

Grupo rilataj komponantoj:

Grupo rilataj komponentoj kiuj estas parto de la sama subsistemo aŭ havas fortajn elektrajn interagojn. Ĉi tio reduktas spurlongon kaj minimumigas signalmalfortiĝon.

Konservu altrapidajn komponantojn proksime:

Metu altrapidajn komponantojn, kiel altfrekvencajn oscilatorojn aŭ mikroregilojn, proksime unu al la alia por minimumigi spurlongojn kaj certigi taŭgan signalan integrecon.

Minimumu la spurlongon de kritikaj signaloj:

Minimumu la spurlongon de kritikaj signaloj por redukti disvastigprokraston kaj signalmalfortiĝon. Metu ĉi tiujn komponantojn kiel eble plej proksime.

Apartaj sentemaj komponantoj:

Apartigu bru-sentemajn komponentojn, kiel analogajn komponentojn aŭ malaltnivelajn sensilojn, de alt-potencaj aŭ bruaj komponentoj por minimumigi interferon kaj konservi signalintegrecon.

Konsideru malkunligi kondensiloj:

Metu malkunligajn kondensiloj kiel eble plej proksime al la potencaj pingloj de ĉiu komponanto por provizi puran potencon kaj minimumigi tensiajn fluktuojn. Ĉi tiuj kondensiloj helpas stabiligi la elektroprovizon kaj redukti bruan kupladon.

5.Simulado kaj Analizaj Iloj por Stak-Up-Dezajno

5.1 3D modeligado kaj simuladsoftvaro:

3D modeligado kaj simuladsoftvaro estas grava ilo por stak-dezajno ĉar ĝi permesas al dizajnistoj krei virtualajn reprezentadojn de PCB-stakoj. La programaro povas bildigi tavolojn, komponentojn, kaj iliajn fizikajn interagojn. Simulante la amasigon, dizajnistoj povas identigi eblajn problemojn kiel signala krucparolado, EMI kaj mekanikaj limoj. Ĝi ankaŭ helpas kontroli la aranĝon de komponantoj kaj optimumigi la ĝeneralan PCB-dezajnon.

5.2 Analizaj iloj pri signala integreco:

Analizaj iloj pri signala integreco estas kritikaj por analizi kaj optimumigi la elektran rendimenton de PCB-stakoj. Tiuj iloj uzas matematikajn algoritmojn por simuli kaj analizi signalkonduton, inkluzive de impedanckontrolo, signalreflektadoj, kaj bruokuplado. Farante simuladon kaj analizon, dizajnistoj povas identigi eblajn signalajn integrecproblemojn frue en la dezajnprocezo kaj fari necesajn alĝustigojn por certigi fidindan signaltranssendon.

5.3 Termikaj analiziloj:

Termikanalizaj iloj ludas gravan rolon en stak-dezajno per analizado kaj optimumigado de termika administrado de PCBoj. Tiuj iloj simulas varmodissipadon kaj temperaturdistribuon ene de ĉiu tavolo de la stako. Precize modeligante potencajn disipadon kaj varmotransigajn vojojn, dizajnistoj povas identigi varmajn punktojn, optimumigi la lokigon de kupraj tavoloj kaj termikaj vojoj, kaj certigi taŭgan malvarmigon de kritikaj komponentoj.

5.4 Dezajno por fabrikebleco:

Dezajno por fabrikebleco estas grava aspekto de stak-dezajno. Estas diversaj programaraj iloj disponeblaj, kiuj povas helpi certigi, ke la elektita amasigo povas esti fabrikita efike. Ĉi tiuj iloj disponigas religon pri la farebleco atingi la deziratan amasigon, konsiderante faktorojn kiel materiala havebleco, tavoldikeco, produktadprocezo kaj produktadkosto. Ili helpas al dizajnistoj fari informitajn decidojn por optimumigi stakadon por simpligi fabrikadon, redukti la riskon de prokrastoj kaj pliigi rendimentojn.

6.Paŝo-post-paŝa Dezajna Procezo por 16-Tavolaj PCB

6.1 Kolekto de komencaj postuloj:

En ĉi tiu paŝo, kolektu ĉiujn necesajn postulojn por 16-tavola PCB-dezajno. Komprenu la funkciecon de la PCB, postulatan elektran rendimenton, mekanikajn limojn kaj iujn ajn specifajn desegnajn gvidliniojn aŭ normojn, kiujn oni devas sekvi.

6.2 Komponanto-atribuo kaj aranĝo:

Laŭ postuloj, asignu komponantojn sur la PCB kaj determini ilian aranĝon. Konsideru faktorojn kiel signala integreco, termikaj konsideroj kaj mekanikaj limoj. Grupu komponantojn bazitajn sur elektraj trajtoj kaj metu ilin strategie sur la tabulo por minimumigi interferon kaj optimumigi signalfluon.

6.3 Stak-suprendezajno kaj tavoldistribuo:

Determinu la stakan dezajnon por la 16-tavola PCB. Konsideru faktorojn kiel dielektrika konstanto, varmokondukteco kaj kosto por elekti la taŭgan materialon. Asignu signalon, potencon kaj grundajn aviadilojn laŭ elektraj postuloj. Metu terajn kaj potencajn aviadilojn simetrie por certigi ekvilibran stakon kaj plibonigi signalan integrecon.

6.4 Signal-vojigo kaj vojigo-optimumigo:

En ĉi tiu paŝo, signalspuroj estas senditaj inter komponentoj por certigi bonordan impedanckontrolon, signalintegrecon, kaj minimumigi signalinterparoladon. Optimumu vojigon por minimumigi la longecon de kritikaj signaloj, eviti kruci sentemajn spurojn, kaj konservi apartigon inter altrapidaj kaj malaltrapidaj signaloj. Uzu diferencigajn parojn kaj kontrolitajn impedancajn vojajn teknikojn kiam necesas.

6.5 Intertavolaj ligoj kaj per allokigo:

Planu la lokigon de konektaj vojoj inter tavoloj. Determinu la taŭgan per tipo, kiel tra truo aŭ blinda truo, surbaze de tavoltransiroj kaj komponentkonektoj. Optimumigu per aranĝo por minimumigi signalajn reflektojn, impedancmalkontinuecojn, kaj konservi eĉ distribuon sur la PCB.

6.6 Fina dezajnokonfirmo kaj simulado:

Antaŭ fabrikado, fina dezajnokonfirmo kaj simulaĵoj estas faritaj. Uzu simulajn ilojn por analizi PCB-dezajnojn por signala integreco, potenca integreco, termika konduto kaj fabrikebleco. Kontrolu la dezajnon kontraŭ komencaj postuloj kaj faru necesajn ĝustigojn por optimumigi rendimenton kaj certigi fabrikeblecon.

Kunlaboru kaj komunikas kun aliaj koncernatoj kiel elektraj inĝenieroj, mekanikaj inĝenieroj kaj fabrikaj teamoj dum la dezajna procezo por certigi, ke ĉiuj postuloj estas plenumitaj kaj eblaj problemoj estas solvitaj. Regule reviziu kaj ripetadu dezajnojn por korpigi retrosciojn kaj plibonigojn.

7.Industriaj Plej Bonaj Praktikoj kaj Kazaj Studoj

7.1 Sukcesaj kazoj de 16-tavola PCB-dezajno:

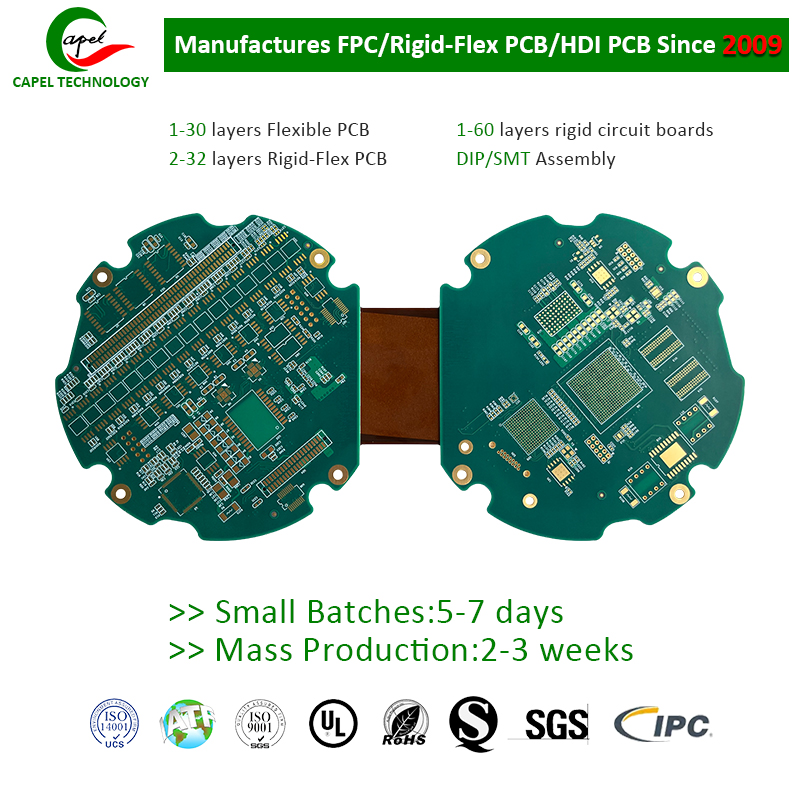

Kaza studo 1:Shenzhen Capel Technology Co., Ltd. sukcese desegnis 16-tavolan PCB por altrapida reto-ekipaĵo. Zorge konsiderante signalan integrecon kaj potencodistribuon, ili atingas superan rendimenton kaj minimumigas elektromagnetan interferon. La ŝlosilo al ilia sukceso estas plene optimumigita stak-suprendezajno uzanta kontrolitan impedanca vojteknologio.

Kaza studo 2:Shenzhen Capel Technology Co., Ltd. desegnis 16-tavolan PCB por kompleksa medicina aparato. Uzante kombinaĵon de surfaca monto kaj tra-truaj komponentoj, ili atingis kompaktan sed potencan dezajnon. Zorgema lokigo de komponantoj kaj efika vojigo certigas bonegan signalan integrecon kaj fidindecon.

7.2 Lernu el malsukcesoj kaj evitu kaptilojn:

Kaza studo 1:Kelkaj pcb-fabrikistoj renkontis signalajn integrecproblemojn en la 16-tavola PCB-dezajno de komunika ekipaĵo. La kialoj de fiasko estis nesufiĉa konsidero de impedanckontrolo kaj manko de bonorda grundaviadilo distribuo. La lernita leciono estas zorge analizi signalajn integrecpostulojn kaj plenumi striktajn gvidliniojn pri dezajnaj kontrolo de impedanco.

Kaza studo 2:Iuj fabrikantoj de pcb alfrontis fabrikajn defiojn kun ĝia 16-tavola PCB pro dezajna komplekseco. La troa uzo de blindaj vojoj kaj dense pakitaj komponentoj kondukas al fabrikado kaj kunigo malfacilaĵoj. La lernita leciono estas atingi ekvilibron inter dezajna komplekseco kaj fabrikebleco konsiderante la kapablojn de la elektita PCB-fabrikisto.

Por eviti malfacilaĵojn kaj faŭltojn en 16-tavola PCB-dezajno, estas grave:

a.Tute komprenu la postulojn kaj limojn de la dezajno.

b.Stacked-agordoj, kiuj optimumigas signalan integrecon kaj potenco-distribuon. c.Carefully distribuu kaj aranĝu komponantojn por optimumigi agadon kaj simpligi fabrikadon.

d.Ensure taŭgaj enrutaj teknikoj, kiel kontroli impedancon kaj eviti troan uzon de blindaj vojoj.

e.Kunlaboru kaj komuniki efike kun ĉiuj koncernatoj implikitaj en la dezajnprocezo, inkluzive de elektraj kaj mekanikaj inĝenieroj kaj fabrikaj teamoj.

f.Perform ampleksan dezajnokonfirmon kaj simuladon por identigi kaj korekti eblajn problemojn antaŭ fabrikado.

Afiŝtempo: Sep-26-2023

Reen